【FMC FMC+ Loopback】TERASIC友晶FMC FMC+ Loopback

所屬分類(lèi)友晶Terasic開(kāi)發(fā)板

立即購(gòu)買(mǎi)

- 產(chǎn)品描述

- 產(chǎn)品參數(shù)

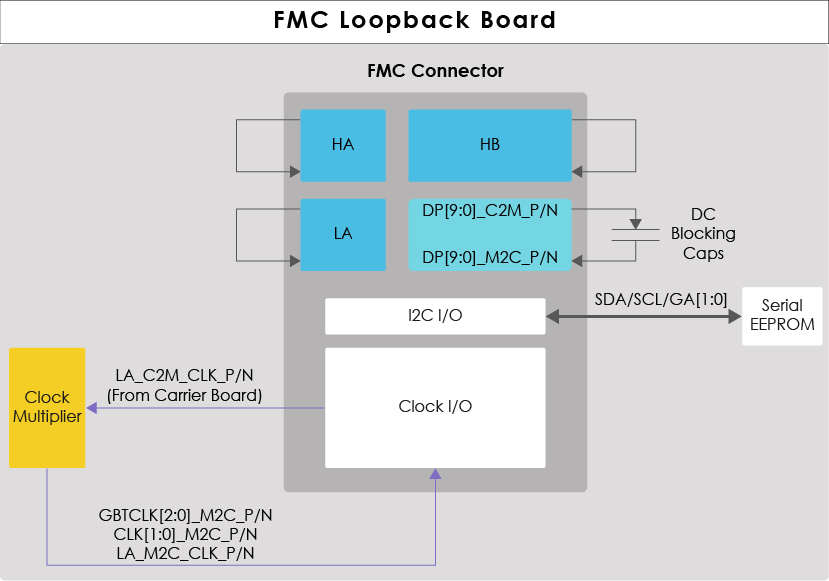

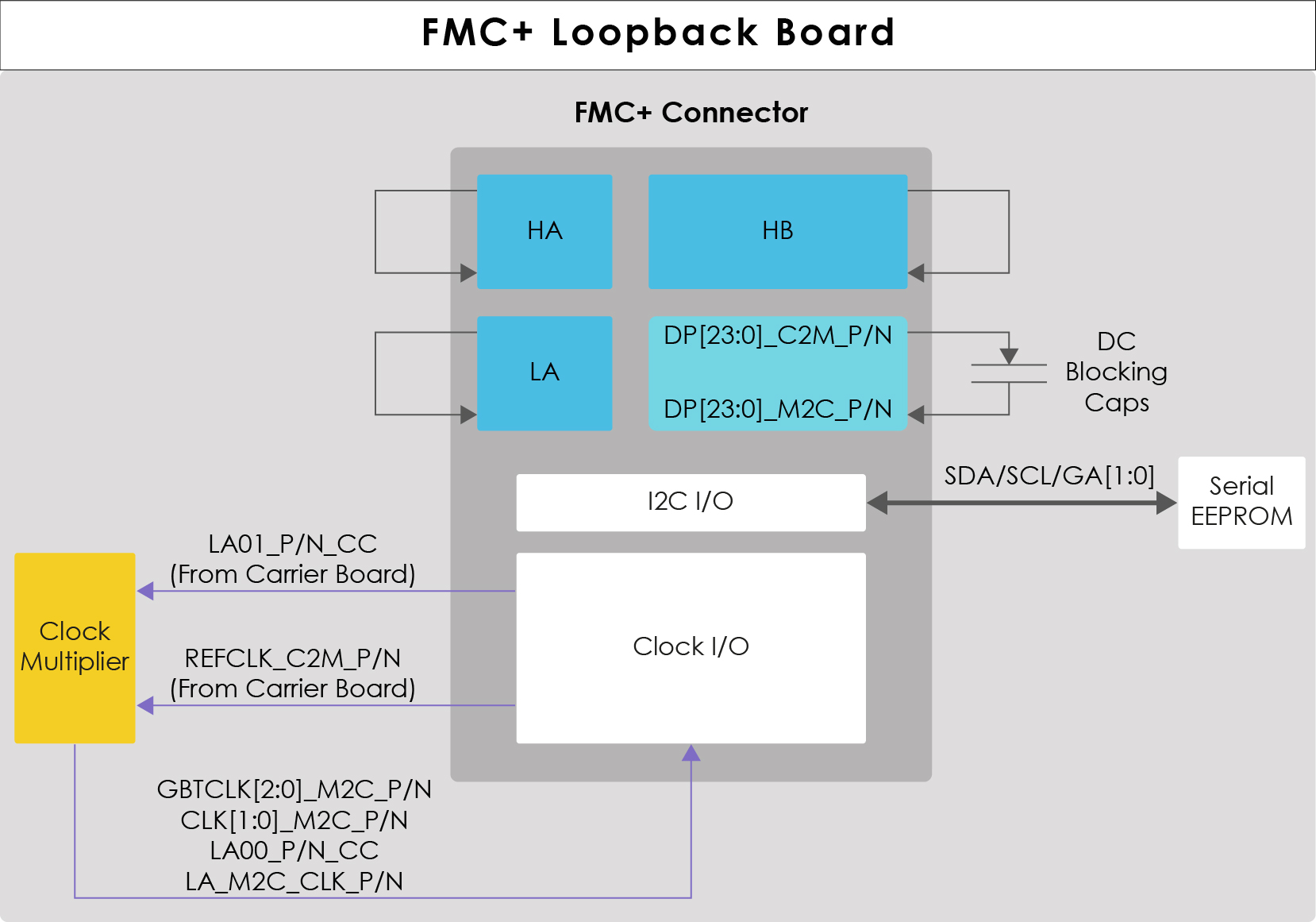

The FMC/FMC+ loopback 子卡是專(zhuān)為帶有相容于Vita57.1 / 57.4 standard 的FMC/FMC+ 連接器的FPGA主版進(jìn)行I/O測(cè)試使用. 這兩個(gè)子卡能將FMC/FMC+ 連接器多數(shù)的I/O loopback, 包括了HA,HB,LA, DP and clock等這幾個(gè)群組的I/O. 使用者可以將這兩塊子卡用于帶有high pin count(HPC) or low pin count(LPC) FMC/FMC+連接器主版上. 有了這兩塊子卡,開(kāi)發(fā)者可以快速測(cè)試FPGA的高速與低速I(mǎi)/O的傳輸速度,以及驗(yàn)證I/O的功能是否正常.

除此之外卡上還有提供Ultra-Low Jitter Clock Multiplier, 能接從主板經(jīng)由FMC/FMC+連接器輸出的clock, 然后扇出到FMC/FMC+連接器的clock pin (CLK_M2C_P/N 及GBTCLK_M2C_P/N )并傳輸回主板. 關(guān)于FMC/FMC+連接器上的I2C 介面, 使用者可以藉由讀寫(xiě)板子上的EEPROM來(lái)驗(yàn)證.

Block Diagram

Connection