【DE10-Agilex】TERASIC友晶DE10-Agilex開(kāi)發(fā)板

所屬分類(lèi)友晶Terasic開(kāi)發(fā)板

立即購(gòu)買(mǎi)

- 產(chǎn)品描述

- 產(chǎn)品參數(shù)

argeting the compute and acceleration needs from the edge to the core to the cloud, Terasic’s DE10-Agilex accelerator is purpose-designed to meet the ever-increasing demands for acceleration, compute, and fast data movement.

The DE10-Agilex is based on the powerful Intel? Agilex? FPGA to obtain speed and power breakthrough, with 40% higher performance, 40% lower power for equivalent performance. The accelerator includes PCI Express Gen 4.0 x16, two 200G QSFP-DD connectors and offers 32GB of DDR4 up to 680Gbps bandwidth to provide adaptable acceleration, maximum throughput and highly customizable processing of data for compute intensive applications.

The DE10-Agilex fully supports Intel? Open VINO? toolkit, OpenCL? BSP and Intel? oneAPI Toolkits to provide optimal Computer Vision and Deep Learning solutions. Our clients' systems can achieve highest computing performance and lowest cost for their Data Center and AI applications by leveraging the Agilex? FPGA on DE10-Agilex accelerator.

Target Markets:

|

|  |

|  |

|  |

|  |

| High Frequency Trading |

| High Performance Computing |

| Instrumentation |

| Military & Defence |

| Broadcast & Video

|

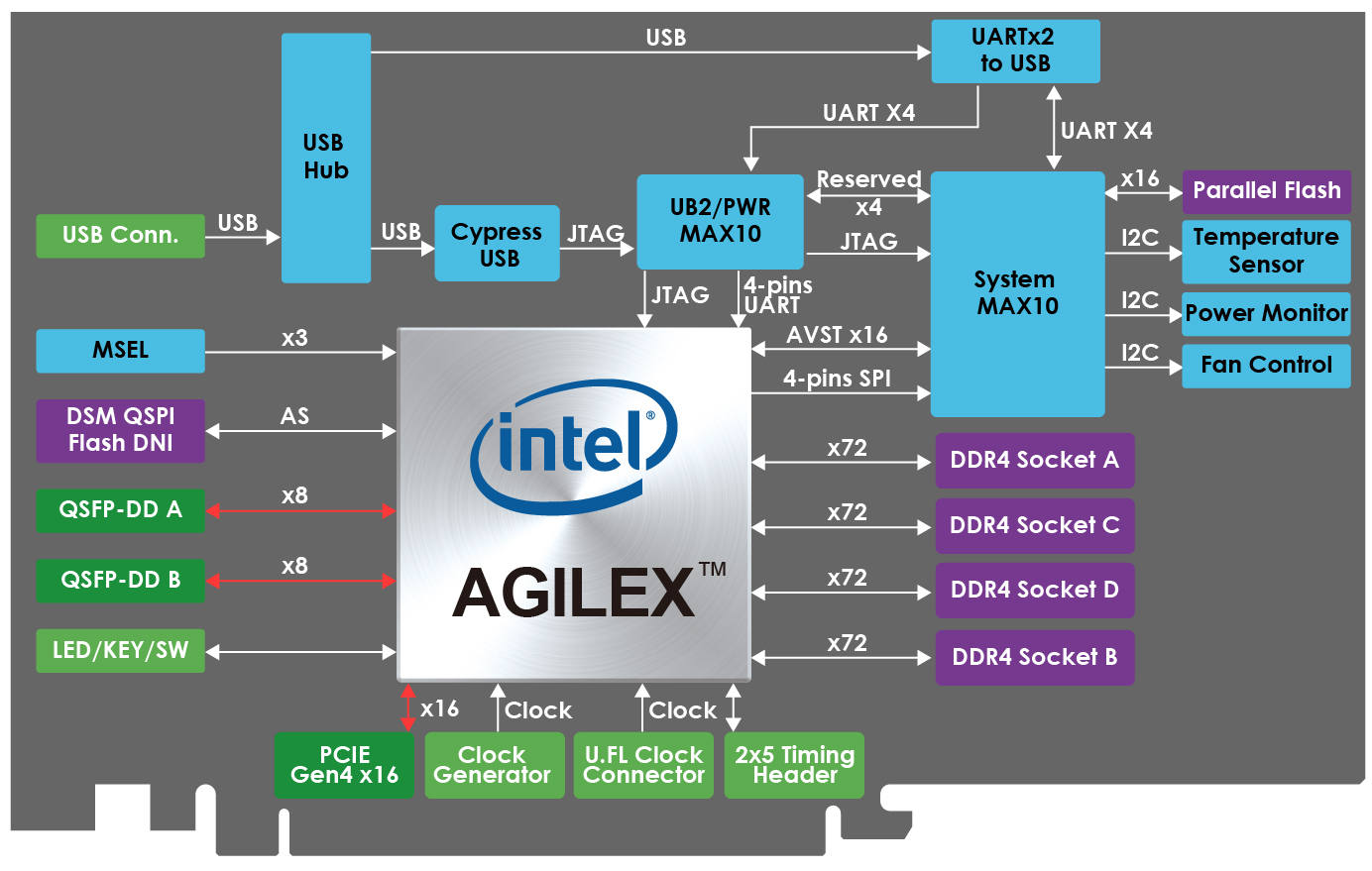

FPGA

FPGA Configuration

Memory

Communication and Expansion

Two QSFPDD connectors for 200/100/40/25/10 GbE network interface

PCI Express Gen4 x16 edge connector (includes PCIe drivers)

2x5 Timing expansion header

UART

Others

Supported Memory Modules for Sockets

Block Diagram

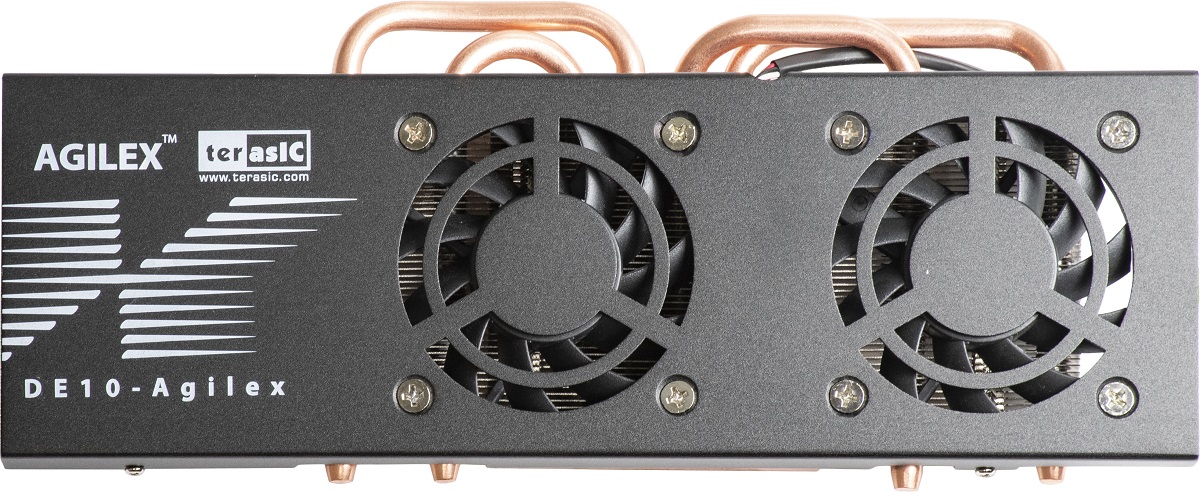

Heatsink

Active Heatsink

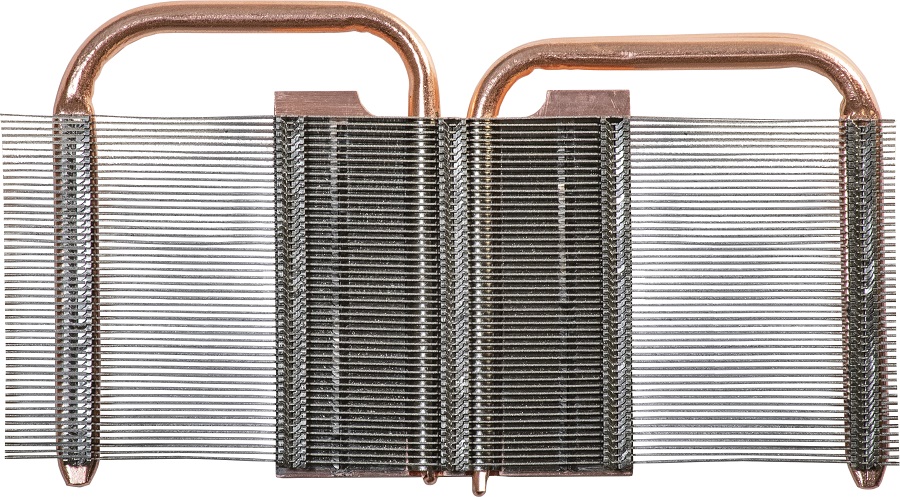

Passive Heatsink(Optional)